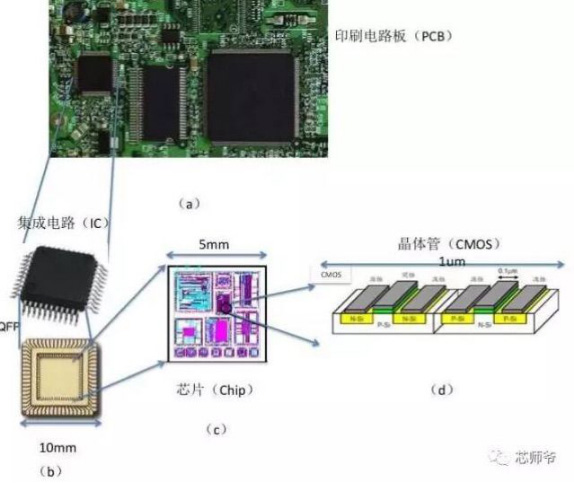

集積回路は、小型の電子デバイスまたはコンポーネントです。 特定のプロセスを使用して、回路に必要なトランジスタ、抵抗器、コンデンサ、インダクタ、およびその他のコンポーネントと配線を相互接続し、小型または数個の小型半導体ウェーハまたは誘電体基板上に作成し、チューブシェルにパッケージ化して、必要な回路機能を備えたミニチュア構造になります。 これらのコンポーネントはすべて構造的に全体に統合されており、電子部品は小型化、低消費電力、インテリジェンス、高信頼性に向けた大きな一歩となっています。 回路内の文字「IC」で示されます。 集積回路の発明者は、ジャック・キルビー(ゲルマニウム(Ge)ベースの集積回路)とロバート・ノイス(シリコン(Si)ベースの集積回路)です。 今日の半導体産業のほとんどのアプリケーションは、シリコンベースの集積回路です。

集積回路とは一体何でしょうか?プロセッサを例として、その製造プロセスを見てみましょう。

簡単に言えば、プロセッサの製造プロセスは、砂原料(石英)、シリコンインゴット、ウェーハ、リソグラフィー(リソグラフィー)、エッチング、イオン注入、金属蒸着、金属層、相互接続、ウェーハテストと切断、コアパッケージング、グレードテスト、パッケージングとマーケティング、および他の多くのステップに大別でき、各ステップにはより詳細なプロセスが含まれています。

砂:シリコンは地殻で2番目に豊富な元素であり、脱酸素砂(特に石英)には、半導体製造産業の基礎でもある二酸化ケイ素(SiO2)の形で最大25%のシリコンが含まれています。

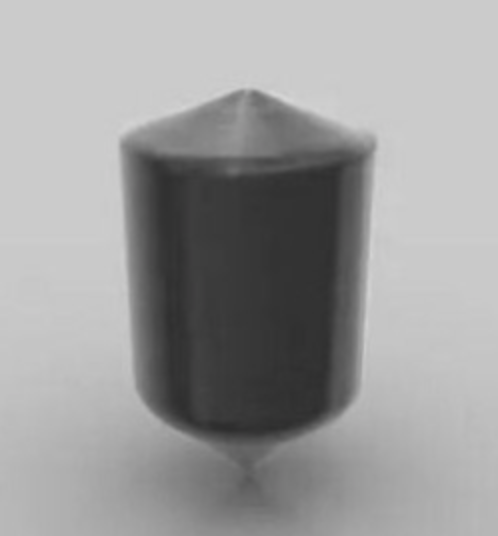

シリコン溶解:12インチ/300mmウェハレベル、以下同様。半導体製造品質に使用できるシリコンは、多段階の精製を経て得られ、学名は電子グレードシリコン(EGS)と呼ばれ、シリコン原子100万個に不純物原子は多くても1個含まれます。この写真は、シリコンの精製と製錬によって大きな結晶が得られ、最終的にシリコンのインゴット(インゴット)が得られる様子を示しています。

単結晶シリコンインゴット:全体が基本的に円筒形で、重量は約100kgで、シリコンの純度は99.9999%です。

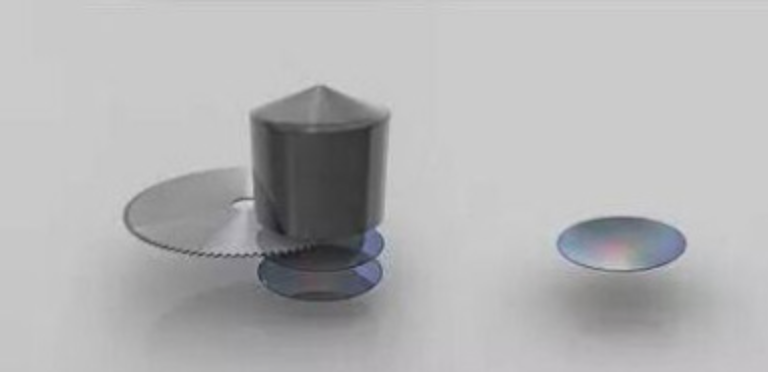

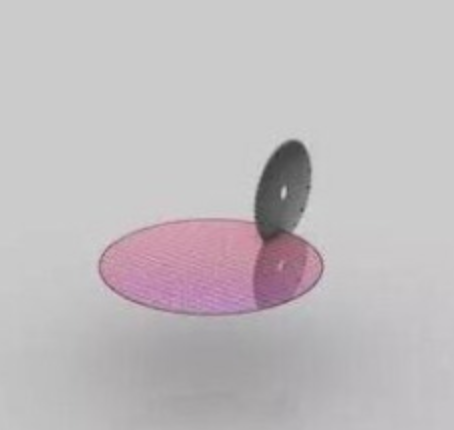

インゴット切断:単一のシリコンウェーハを水平に円形に切断すること、これは私たちがしばしばウェーハと呼ぶものです。 ちなみに、ウェーハがすべて丸い理由がわかりましたよね?

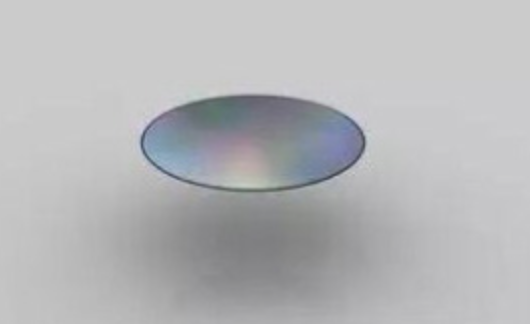

ウェーハ:カットされたウェーハはほぼ完璧になるように研磨され、表面は鏡としても使用できます。 実際、Intelはそのようなウェーハ自体を製造していませんが、サードパーティの半導体会社から直接完成品を購入し、現在主流の45nm HKMG(high-Kメタルゲート)などの独自の生産ラインを使用してさらなる処理を行っています。 Intelが設立当初に使用したウェーハサイズはわずか2インチ/ 50mmであったことは言及する価値があります。

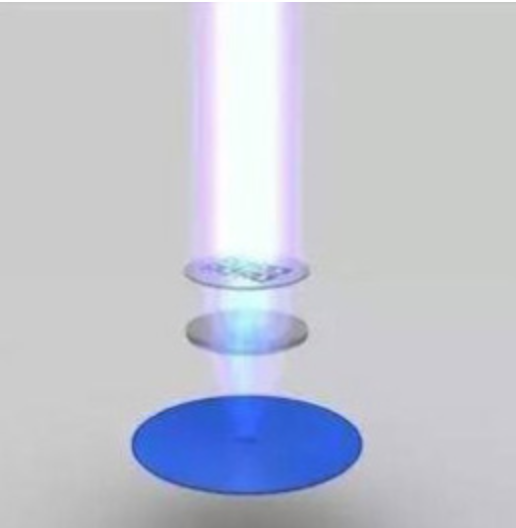

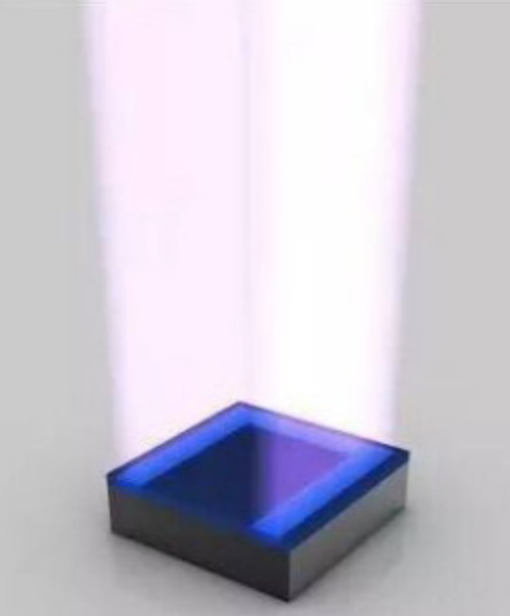

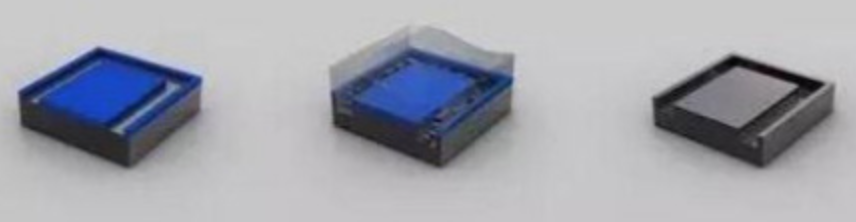

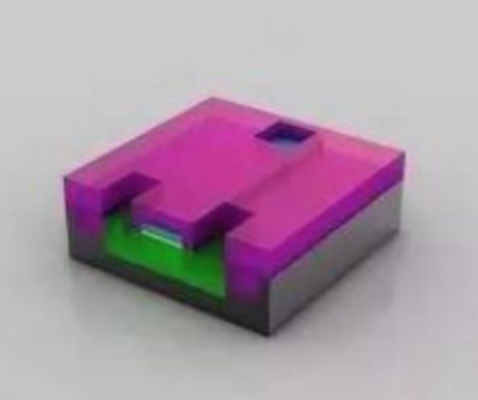

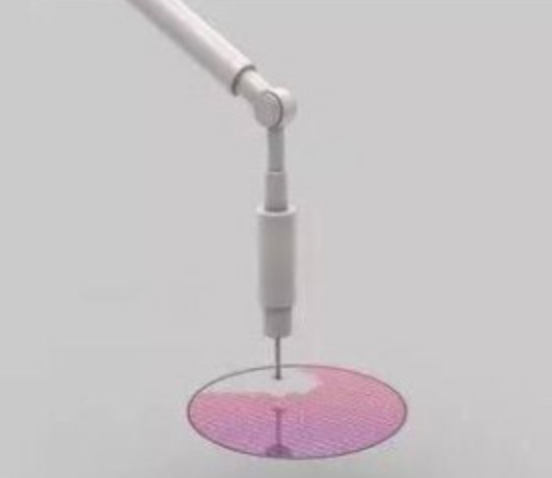

フォトレジスト:図の青い部分は、従来のフィルムの製造に使用されるものと同様に、ウェーハの回転中に注がれるフォトレジスト液です。 ウェーハの回転により、フォトレジストを非常に薄く、非常に平らに置くことができます。

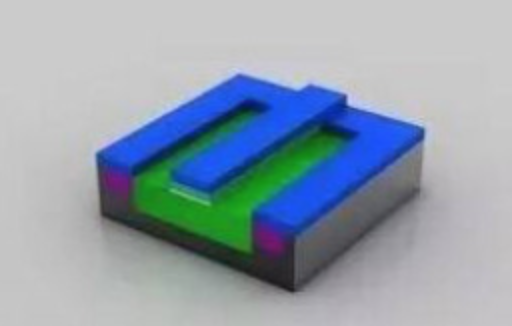

リソグラフィ:フォトレジスト層はマスクを通して紫外線(UV)にさらされて可溶性になり、その間に化学反応は機械式カメラのシャッターが押された瞬間の膜の変化に似ています。 マスクは事前に設計された回路パターンで印刷され、それを通して紫外線がフォトレジスト層を照らし、マイクロプロセッサの回路パターンの各層を形成します。 一般に、ウェーハ上に得られる回路パターンは、マスク上のパターンの4分の1である。

リソグラフィー: これにより、トランジスタのレベルは 50 ~ 200 ナノメートルになります。 1 枚のウェーハから何百ものプロセッサをダイシングすることができますが、ここからは 1 つに絞り、トランジスタなどのコンポーネントを作成する方法を示します。トランジスタはスイッチとして機能し、電流の方向を制御します。現在、トランジスタは非常に小さくなり、ピンの頭に約 3,000 万個が収まるようになりました。

溶解したフォトレジスト:フォトリソグラフィプロセス中に、紫外線にさらされたフォトレジストが溶解し、除去後に残るパターンはマスクと一致します。

エッチング:化学薬品を使用してウェーハの露出部分を溶解し、残りのフォトレジストはエッチングしてはならない部分を保護します。

フォトレジストの除去: エッチングが完了すると、フォトレジストの役割は完了したと宣言され、すべての除去後に設計された回路パターンが表示されます。

第四段階

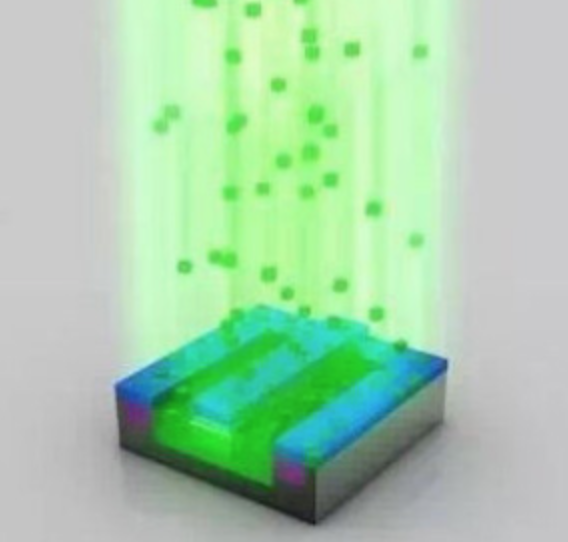

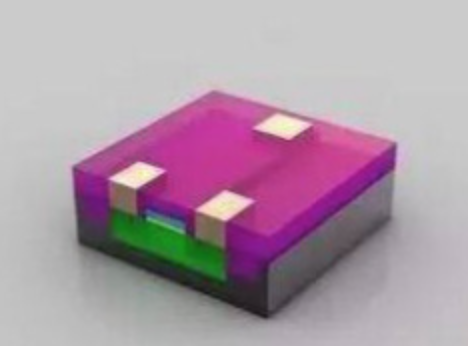

フォトレジスト:フォトレジスト(青い部分)を再度注ぎ、次にフォトリソグラフィーを行い、露光部分を洗い流しても、残りのフォトレジストはイオン化されない材料の部分を保護するために使用されます。

イオン注入: 真空システム内で、ドーピングする原子の加速イオンを固体材料に照射 (注入) し、注入領域に特別な注入層を形成し、これらの領域のシリコンの導電性を変化させます。電場によって加速された後、注入されたイオン流の速度は時速 300,000 キロメートルを超えることがあります。

フォトレジストの除去:イオン注入が完了した後、フォトレジストも除去され、注入領域(緑色の部分)もドープされ、異なる原子が注入されます。 このときの緑色は以前と異なりますのでご注意ください。

第五阶段

第五段階

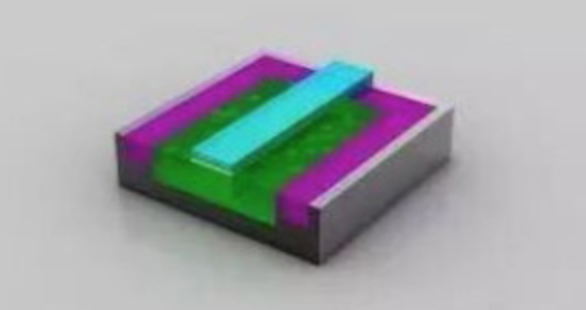

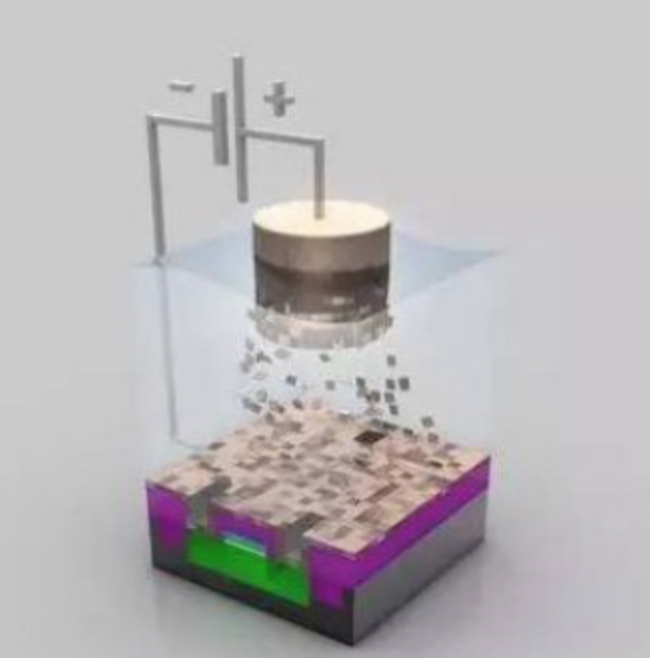

メッキ:硫酸銅の層をウェーハにメッキして、銅イオンをトランジスタに沈殿させます。 銅イオンは正極(アノード)から負極(カソード)に移動します。

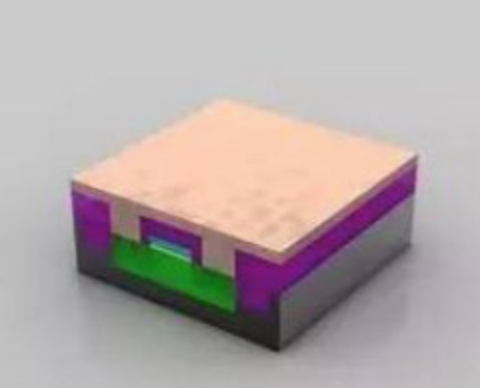

銅層:電気めっき後、銅イオンがウェーハの表面に堆積し、薄い銅層を形成します。

第六段階

研磨:余分な銅を研磨する、つまりウェーハの表面を研磨します。

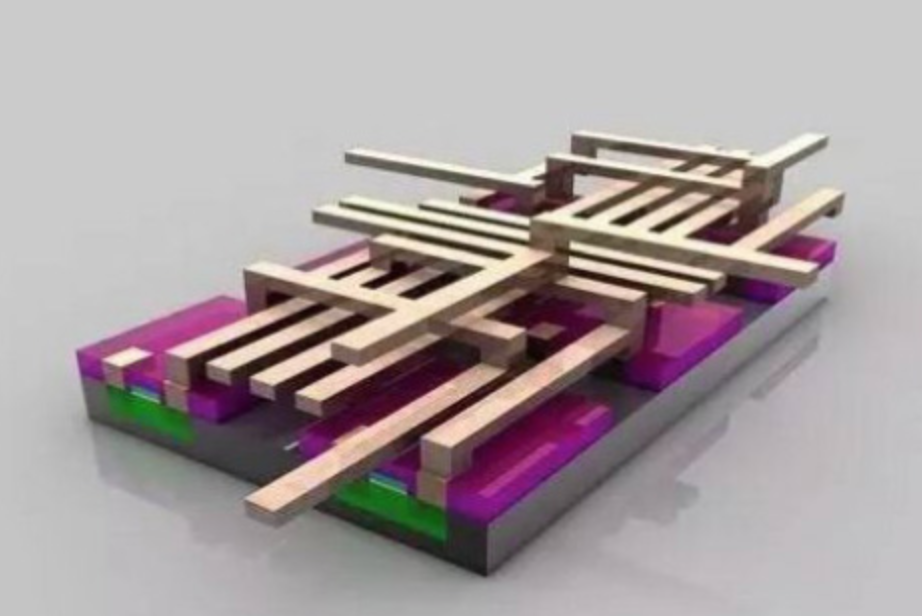

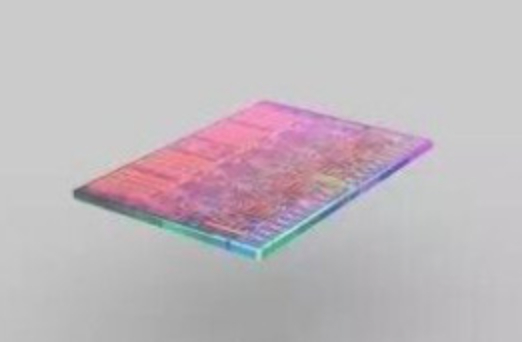

金属層: トランジスタ レベル、6 つのトランジスタの組み合わせ、約 500 ナノメートル。複合相互接続金属層は、それぞれのプロセッサが必要とするさまざまな機能に応じて、さまざまなトランジスタ間に形成されます。チップの表面は非常に滑らかに見えますが、実際には20層以上の複雑な回路が含まれており、拡大してみると、未来の多層高速道路システムを思わせる非常に複雑な回路網が確認できます。

第七段階

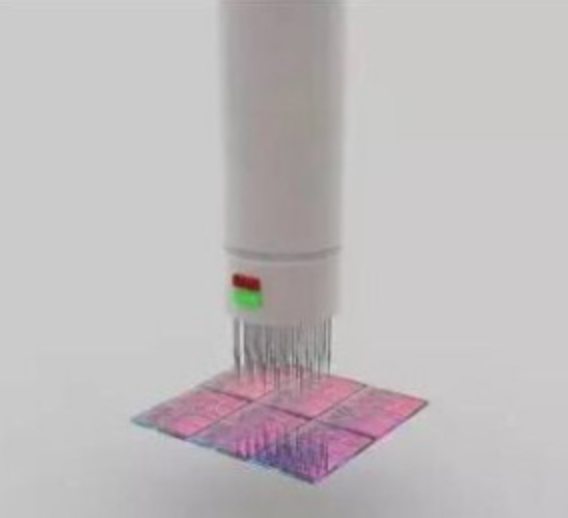

ウェーハテスト:コアレベル、約10 mm / 0.5インチ。 写真は、最初の機能テストを受けているウェーハの一部を示しており、参照回路パターンを使用して各チップを比較しています。

ウェーハスライス(スライス):ウェーハレベル、300mm/12インチ。ウェーハは断片に切断され、それぞれの断片がプロセッサのコア(Die)になります。

欠陥のあるコアを廃棄する:ウェーハレベル。 テスト中に見つかった欠陥のあるカーネルは破棄され、次のステップのためにそのまま残ります。

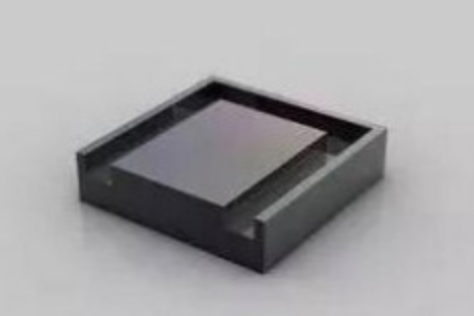

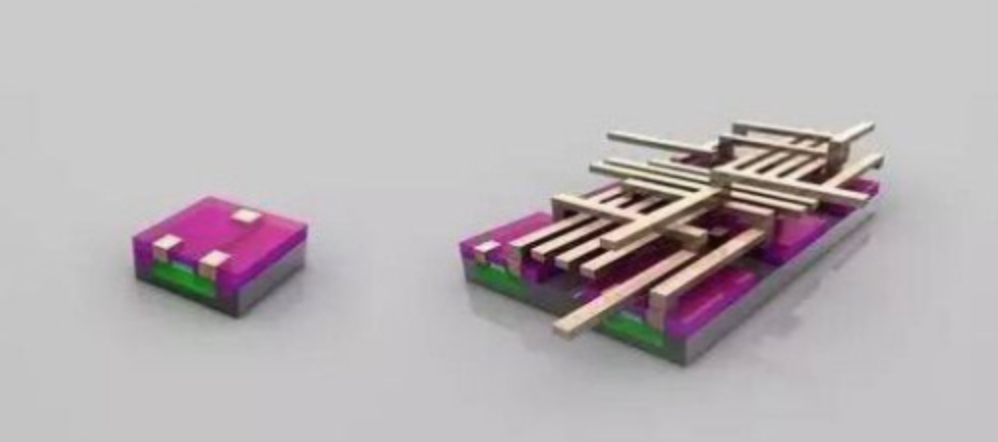

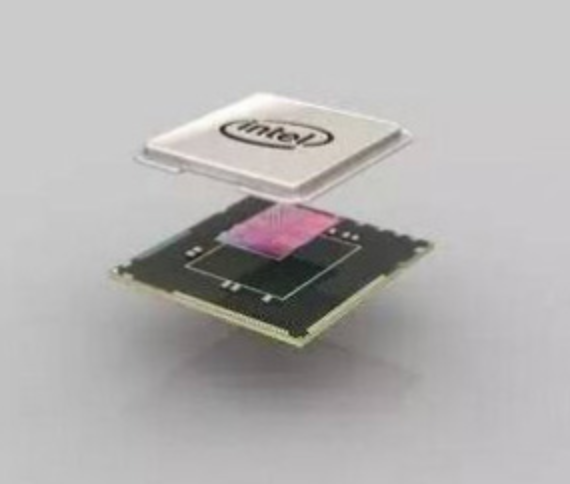

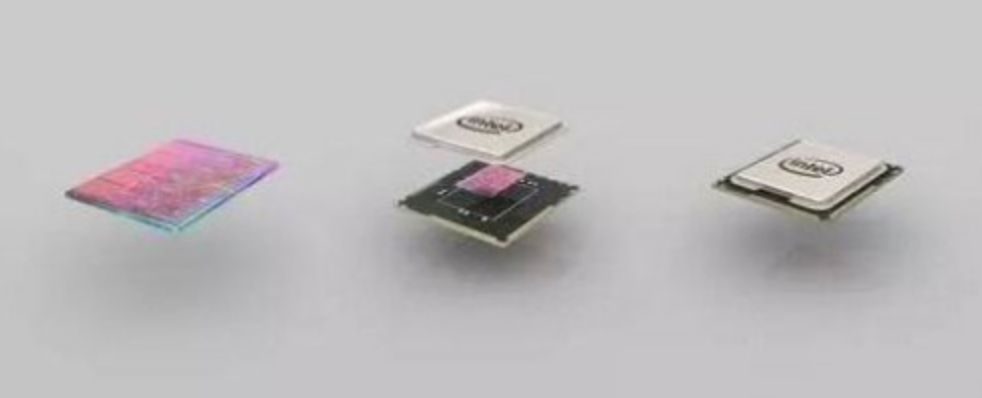

単一カーネル: カーネル レベル。ここに示されているのは、ウェハーから切り取られた単一のコアです。Core i7 のコアです。

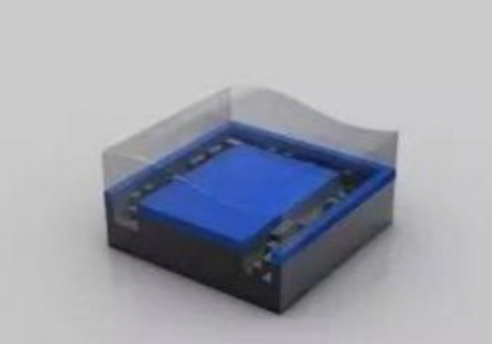

パッケージ:パッケージレベル、20 mm / 1インチ。 基板(基板)、コア、およびヒートシンクが積み重ねられて、プロセッサと見なされるものを形成します。 基板(緑色)はベースとして機能し、PCシステムの他の部分と相互作用するためのプロセッサコアへの電気的および機械的インターフェースを提供します。 ヒートシンク(銀)は、コアから熱を放散する役割を果たします。

プロセッサ:この時点で、フルプロセッサ(ここにCore i7があります)があります。 世界で最もクリーンな部屋で作られた最も複雑な製品は、実際には数百のステップであり、ここに重要なステップのほんの一部があります。

第九段階

レベルテスト:最後のテストでは、最高周波数、消費電力、発熱など、各プロセッサの主要な特性を特定し、最上位のCore i7-975 ExtremeやローエンドモデルのCore i7-920などのプロセッサのレベルを決定できます。

梱包:グレードテストの結果に応じて、同じグレードのプロセッサーをまとめて出荷します。

小売パッケージ:製造およびテストされたプロセッサは、OEMにバルクで配送されるか、小売市場向けに箱にパッケージ化されます。 ここでもCore i7を例として取り上げます。

第十段階